FPGA-AirHockey — Digital Showdown on Nexys A7

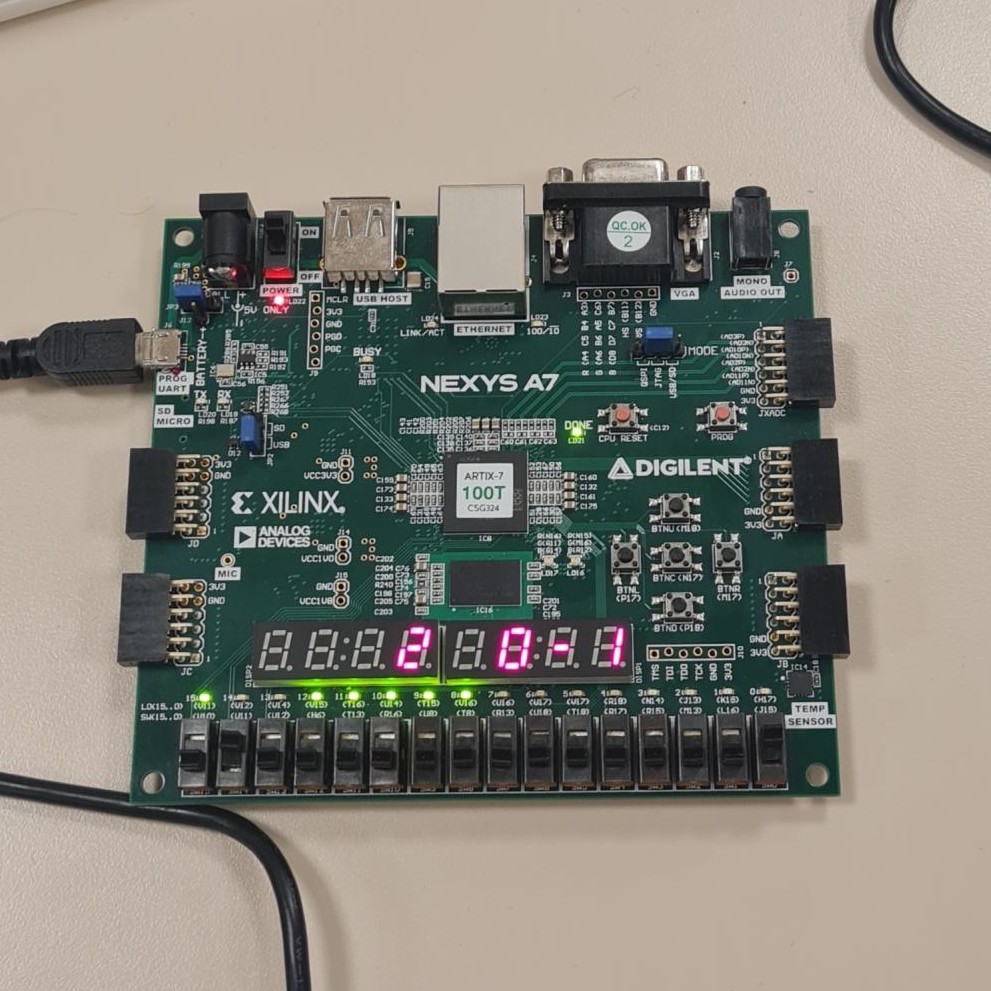

Two-player air-hockey game on a Nexys A7 FPGA: Verilog state machine drives a 5×5 LED rink and real-time score displays.

GitHub Repo Design Diagrams (PDF)

1 · Overview & Motivation

FPGA-AirHockey brings the classic arcade game to digital hardware: a 5 × 5 LED “rink,” dual seven-segment scoreboards, and responsive two-button controls—all written in pure Verilog and deployed on a Digilent Nexys A7.

Originally built for CS303 – Logic & Digital System Design (Sabancı University, Fall 2023-24), the goal was to master:

- Finite-state machine (FSM) design for interactive gameplay

- Hardware debouncing & clock division for clean timing

- Simulation-driven development before FPGA synthesis

2 · System Architecture

The design is modular:

| Module | Role |

|---|---|

clk_divider.v | Lowers the 100 MHz board clock to game-friendly ticks |

debouncer.v | Generates single clean pulses from push-buttons |

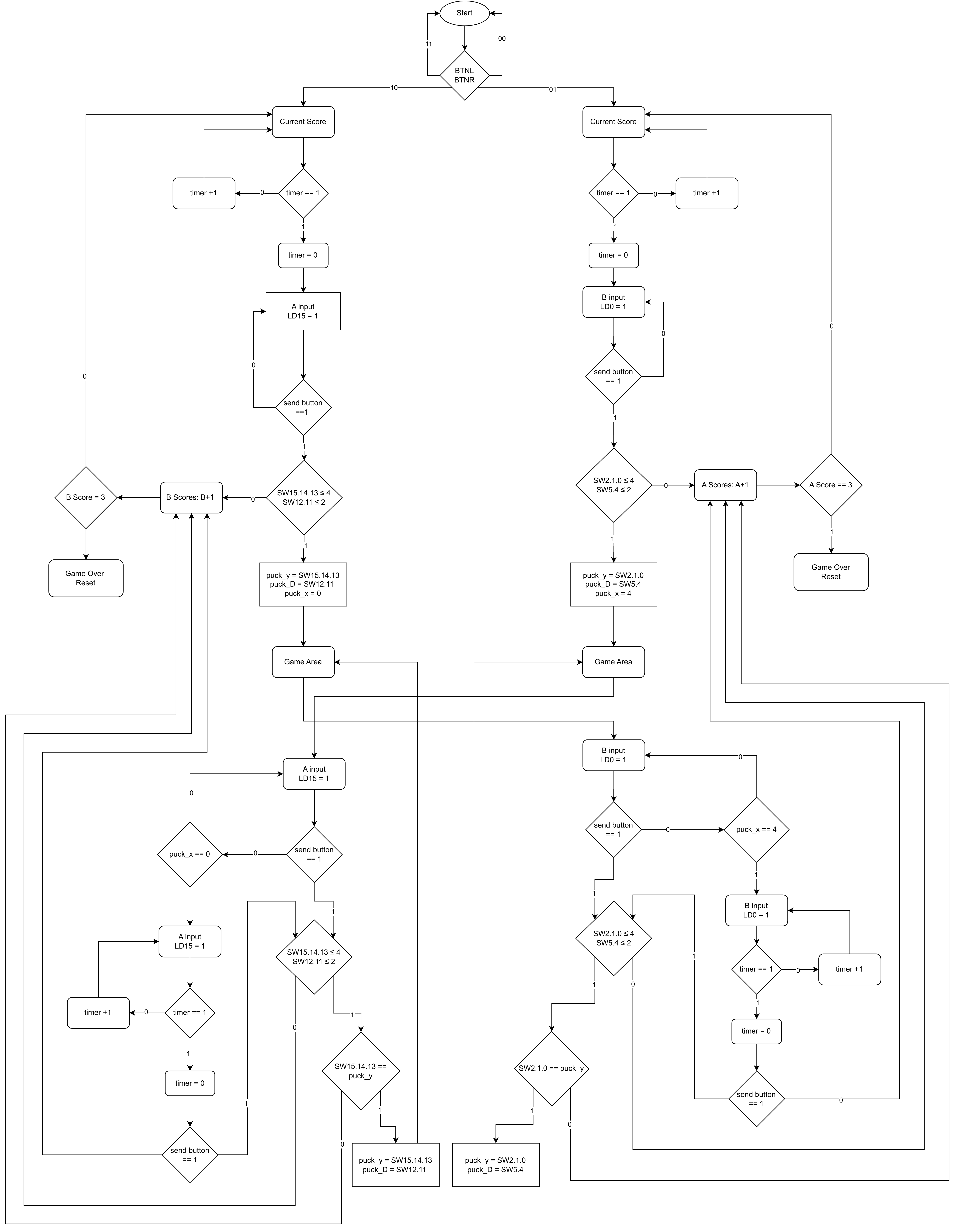

hockey_fsm.v | One-hot FSM handling serves, returns, goals, victory |

ssd_driver.v | Time-multiplexes 8 seven-segment digits for scores/coords |

top_airhockey.v | Glue logic, pin assignments (see project.xdc) |

All RTL is simulation-verified via hockey_tb.v before synthesis.

3 · Gameplay Logic

- Serve – Player A hits BTNL; puck traverses the LED grid toward Player B.

- Return – Player B presses BTNR when the puck reaches their chosen coordinate (set by slide switches).

- Score – Missed returns award a goal; score flashes, turns swap.

- Win – First to the configurable goal limit (default = 3) triggers a celebratory LED blink pattern.

Timing is governed by a selectable puck speed (0.5 s or 1 s per cell) via PUCK_SPEED_SEL.

4 · Key Features

- Interactive Two-Player Mode — Simple BTNL/BTNR buttons act as paddles

- Dynamic Visuals — 25 LEDs animate puck motion; seven-segment HUD shows

[X,Y]and running scores - Customisable Gameplay — On-board switches tweak puck speed and goal limit

- Robust Timing — Clean debounced inputs, parameterised clock divider, synchronous FSM

- Portable HDL — Vendor-agnostic Verilog; only the constraint file is board-specific

5 · Build & Deployment

| Step | Action |

|---|---|

| Simulate | vivado -mode tcl -source run_tb.tcl (runs hockey_tb.v) |

| Synthesis | Flow Navigator ▶ Run Synthesis |

| Implement | Flow Navigator ▶ Run Implementation |

| Bitstream | Flow Navigator ▶ Generate Bitstream |

| Program | Connect Nexys A7 via JTAG ➜ Program Device… |

A ready-made Vivado project (FPGA-AirHockey.xpr) is included for 2023.1+.

6 · Demo

Completed for CS303 — Logic & Digital System Design (Fall 2023–24).